Snåla chip för trådlös Gbit/s-kommunikation

Panasonic meddelar att de har utvecklat en uppsättning LSI-chips för höghastighetskommunikation vid 60 GHz som förbrukar mindre än 1 watt, avsedda för trådlösa, mobila prylar.

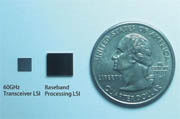

Foto: Business Wire

Panasonic Corporation meddelar att man har utvecklat två nya LSI-chip för multigigabit millimetervågs, trådlös kommunikation som uppges uppnå branschens lägsta effektförbrukning på mindre än 1 watt genom en ny arkitektur för basbandsbearbetning. De ger stöd för WiGig Alliance interoperabilitetsverifiering för trådlös höghastighetskommunikation över 1 Gbit/s i 60 GHz-området och som bidrar till IEEE80211ad-standardiseringen.

Panasonic har tidigare utvecklat CMOS kretsteknik för 60 GHz transceivers och för modem signalbehandlingskretsar. Till dessa adderar nu företaget ytterligare radiokretsar för paketbearbetning som ska förenkla HD-video datadelning/streaming-applikationer för mobila enheter.

Chipen kan byggas in i mobila produkter, till exempel smartmobiler, som här har krav på en effektförbrukning på under1 watt. Med tekniken ska det gå att överföra en 30 minuter lång komprimerad HD-video till mobila enheter inom 10 sekunder. Den ska också tillåta strömmande latens-fria HD-videouppdateringar direkt från en mobil enhet på en storbilds-TV i realtid.

När det gäller trådlös kommunikation vid höga data överföringshastigheter för mobila enheter finns det enligt Panasonic för närvarande ingen praktisk lösning förutom trådlös LAN-teknik som arbetar vid 2,4 GHz och 5 GHz. Vid 60 GHz trådlös kommunikation har frekvensområdet bara använts av stationära apparater, inte mobila enheter, eftersom bredare frekvensband kräver mer energi och en större chipyta.

Dagens trådlösa LAN-system bygger på IEEE802.11a, 11b, 11g eller 11n-standarder och använder frekvensband vid 2,4 GHz eller 5 GHz, vilket ger en maximal kommunikationshastighet på runt 300 Mbit/s, och i fallet med IEEE802.11n, 100 Mbit/s.

Panasonic uppges redan ha utvecklat en grundläggande 60 GHz radioteknik för mobila enheter. Med den tekniska utvecklingen uppstod behovet av att integrera paketbearbetning av block med låg effektförbrukning såväl som att minska ned kretsarnas storlekar.

De nyutvecklade chipen består av en 60 GHz LSI-transceiver och en basbands-LSI med en ny Media Access Control (MAC) paketbearbetningsteknik. Vanlig MAC-paketbearbetning konsumerar mycket energi när klockfrekvensen ökas för att nå höga hastigheter vid användning av GPUs. En ny styrkretsdesign för höga hastigheter används för att anpassa paketbearbetning och uppnå en optimal kontroll mellan GPU och höghastighets styrkretsar som höjer hastigheten med mer än 20 procent och samtidigt behåller en låg klockfrekvens för processorn. Det resulterar i att chipen kan nå en effektförbrukning på mindre än 1 Watt och samtidigt ge stöd för upp till 2,5 Gbit/s.

Transceiverchipets storlek har minskas med mer än 50 procent, jämfört med den LSI-transceiver som Panasonic utvecklat tidigare, och ger samtidigt stöd för 9 GHz bandbredd i ett licensfritt frekvensspektrum i Japan och Europa i frekvensbandet 60 GHz.

Chipen har realiserats genom att Panasonic använt nya tekniker för MAC paketprocessteknik för låg effektförbrukning som enligt företaget använder en optimal kontroll mellan GPU och snabba styrkretsar för att hålla processorns klockfrekvens låg, och därmed uppnå sub 1 W-prestanda.

Med en LSI-transciever med en bärfrekvens på 60 GHz och med en konventionell LSI-teknik måste separarera varje transistor med ett fåtal 100 μm. För chip som innehåller ett stort antal transistorer medför det en begränsning i att reducera chipens fysiska storlek. För att övervinna den här begränsningen uppger Panasonic uppges här ha utvecklat en ny designteknik som reducerar chipstorleken med mer än 50 procent jämfört med Panasonics tidigare utvecklade LSI-transievers.

Panasonics forsknings- och utvecklingsprojekt har delvis fått stöd av ministeriet för inrikesfrågor och kommunikation i Japan.

Filed under: Utländsk Teknik