SiC trench-komponenter med ultralåg Ron

I denna artikel beskriver Masanori Tanimura, ROHM, nästa generation av planar-MOSFETar i kiselkarbid (SiC), Schottkydioder med trench-struktur samt trench-MOSFETar.

För det första har nyutvecklade SiC planar-MOSFETar undertryckt degraderingen av parasitiska PN-övergångsdioder, till och med om framströmmen tränger djupt in i dessa.

För det andra har SiC-Schottkydioder med nyutvecklade trench-strukturer framgångsrikt uppvisat lägre framspänning jämfört med konventionella SiC-dioder, samtidigt som läckströmmen kunnat hållas på en acceptabel nivå.

För det tredje har nyutvecklade SiC-MOSFETar med en dubbel trench-struktur förbättrat komponenternas tillförlitlighet, och samtidigt bibehållit en ultralåg till-resistans. Orsaken är att den nya strukturen effektivt reducerar den högsta elektriska fältstyrkan i botten av gatens trench, vilket förhindrar genombrott av gate-oxiden.

Nya SiC planar-MOSFET

Några företag har redan påbörjat massproduktion av planar-MOSFETar i SiC för att uppnå lägre switchningsförluster i högvolymsprodukter som konverterare och inverterare. Men on-resistansen ökar när ström flyter in i dessa masstillverkade MOSFETars parasitiska body-dioder.

Det beror på att de parasitiska PN-body-dioderna, med förskjutningen av basplanet, orsakar en ökning av stackningsfelen i 4H-SiC-episkikt och degraderar till-resistansen hos både body-dioder och MOSFETar. Detta utgör ett hinder för användning i komponenter som kräver strömgenomträngning från source till drain, t ex konverterare och inverterare för massprodukter. Men några grupper har rapporterat att de på forskningsnivå inte fått någon degradering av PN-dioderna.

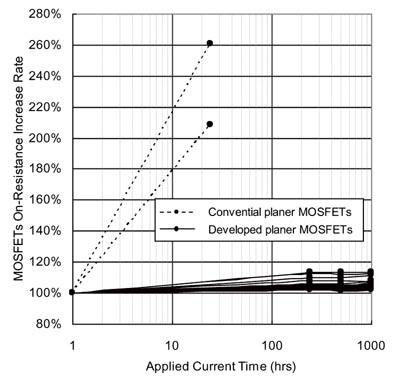

Fig 1. Jämförelse av till-resistansens ökningstakt i MOSFETar efter strömtillslag

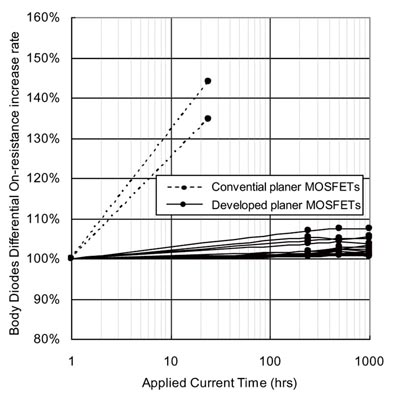

ROHM har utvecklat tillverkningsprocesser för substrat, epitaxi och komponenter som förhindrar degradering av body-dioderna. Fig 1 och 2 visar för MOSFETar on-resistansen resp den differentiella on-resistansen hos body-dioder efter en kontinuerlig strömpenetrering. Här jämförs två konventionella planara MOSFETar med 22 nyutvecklade planara MOSFETar. Blockeringsspänningen hos de utvärderade MOSFETarna är 1 200 V. Till-resistansen är typiskt 0,09 ohm. Storleken på brickan och den aktiva ytan är 13,2 resp 10 mm². Den pålagda kontinuerliga strömmen från source till drain är 8 A.

Fig 2. Jämförelse av den differentiella till-resistansens ökningstakt i body-dioder efter strömtillslag

Efter 24 timmars kontinuerlig ström uppvisar konventionella MOSFETar en drastisk ökning av såväl till-resistansen hos MOSFETarna som den differentiella till-resistansen hos body-dioderna. De nyutvecklade MOSFETarna har däremot undertryckt degraderingen av till-resistansen, t o m efter 1 000 timmars kontinuerlig ström.

SiC-schottky med trench

SiC-Schottkydioder är attraktiva komponenter när det handlar om att reducera switchningsförluster i högspänningsapplikationer. Att minska ledningsförluster är viktigt även för att förbättra verkningsgraden. Men Schottkydioder har högre spänningsfall i framriktningen jämfört med vanliga PN-kiseldioder. Orsaken är att SiC-Schottkydioder behöver höga barriärhöjder för att blockera läckströmmar, detta eftersom SiC har tio gånger högre genombrottsstyrka än kisel. Denna minskning av de elektriska fälten i Schottky-gränssnitt har avgörande betydelse för SiC-Schottkydioder.

ROHM har föreslagit Schottkydioder med trench-struktur för att uppnå ett lägre spänningsfall i framriktningen, samtidigt som man bibehåller samma läckström [1].

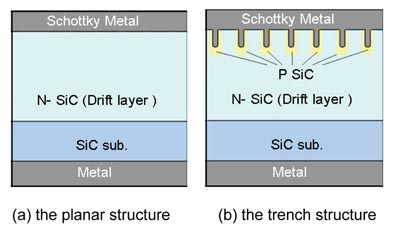

Fig 3 visar ett tvärsnitt genom en 4H-SiC-Schottkydiod med planar- resp trench-struktur. P-trench-området kan undertrycka koncentrationen av elektriska fält i Schottky-gränssnittet.

Fig 3. Tvärsnitt genom Schottkydioder med planar-struktur (a) och trench-strutur(b)

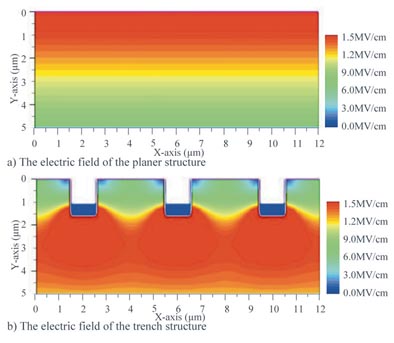

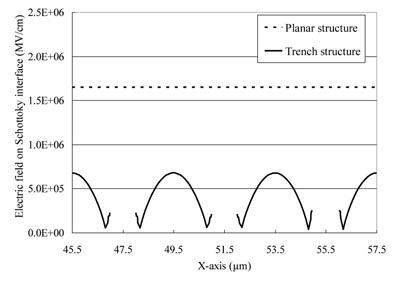

Fig 4 visar simuleringsresultat av hur bias i backriktningen påverkar det elektriska fältets fördelning.

Fig 4. Simulering av hur bias i backriktningen påverkar det elektriska fältets fördelning

Fig 5 visar att den högsta elektriska fältstyrkan i Schottky-gränssnittet hos planar-strukturen och trench-strukturen är 1,65 resp 0,68 MV/cm. Resultaten visar att en lägre barriärhöjd kan uppnås genom att man använder en trench-struktur.

Fig 5. Elektriska fältstyrkan i Schottky-gränssnittet hos planar-strukturen och trench-strukturen

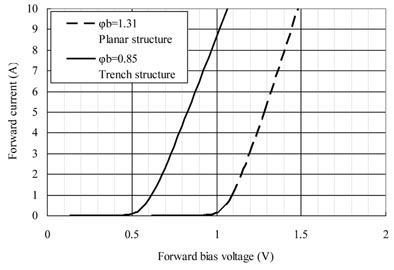

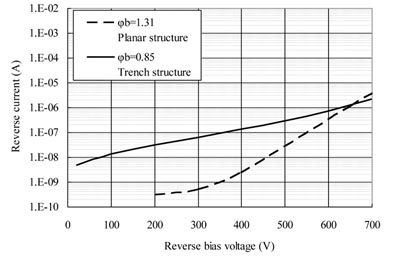

Schottkydioder med planar- och trench-strukturer tillverkades. Barriärhöjden hos dessa strukturer var 1,31 resp 0,85 eV. Trench-djupet är 1,05 µm, och brickans storlek är 3,06 mm². Fig 6 visar I/V-karakteristika för tillverkade dioder som kapslats i TO-220. Tröskelspänningen hos trench-strukturen är 0,48 V lägre än den hos planar-strukturen. Den lägre tröskelspänningen kan minska ledningsförlusterna vid drift i framriktningen. Fig 7 visar I/V-karakteristika i backriktningen. Läckströmmen vid 600 V ligger på samma nivå för båda komponenterna.

Fig 6. I/V-karakteristika i framriktningen för planar- och trench-Schottkydioder

SiC-mosfetar med dubbel-trench

Trench-MOSFETar i SiC kan ha lägre ledningsförluster jämfört med planar-MOSFETar eftersom de senare har JFET-regioner som ökar on-resistansen [2][3]. ROHM har tidigare rapporterat om 790 V SiC trench-MOSFETar med den lägsta Ron vid rumstemperatur. Men dessa trench-MOSFETar hade problem med oxidgenombrott vid trench-bottnen i applikationer med hög drain-source-spänning. För att lösa problemen med gate-oxidgenombrott utvecklades en MOSFET med dubbel trench-strutur (dubbla ”diken eller ”gravar”), som har både source- och drain-trenches [4][5].

Fig 7. I/V-karakteristika i backriktningen för planar- och trench-Schottkydioder

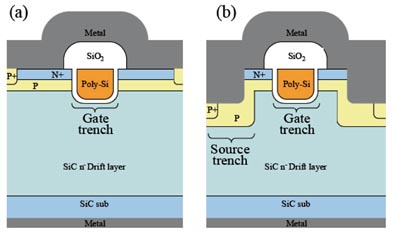

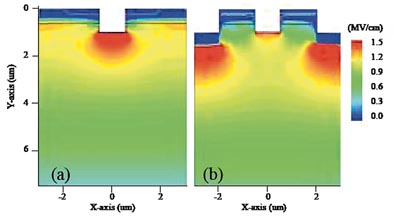

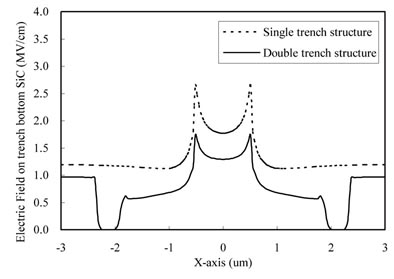

Dessa enkla och dubbla trench-strukturer visas i fig 8a resp 8b. För att undertrycka det elektriska fältet vid gate-oxidens botten har source-trenchen gjorts djupare än gate-trenchen. Fig 9 och Fig 10 visar simuleringsresultat av hur drain-source-bias påverkar fördelningen av det elektriska fältet vid 600 V och en gate-source-spänning på 0 V. I strukturen med enkel-trench är den högsta elektriska fältstyrkan i botten av gate-trenchen 2,66 MV/cm. I strukturen med dubbel-trench har detta värde minskat till 1,66 MV/cm. Djupare source-trenches förhindrar koncentrationen av elektriska fält i botten av gate-trenchen.

Fig 8. Tvärsnitt genom 4H-SiC trench-MOSFETar med source-trench och gate-trench, med enkel trench-struktur (a) och dubbel trench-struktur (b)

MOSFETar med dubbel-trench tillverkas med hjälp av två olika episkikt. Trench-djupet var typiskt 1,0 µm. Gate-oxidens tjocklek var omkring 50 nm.

Den uppmätta kanalmobiliteten på trench-sidoväggarna hos den tillverkade dubbel-trench-MOSFETen var omkring 11 cm²/Vs. Laddningen för oxidgenombrott hos gate-oxiden, uppskattad med CCS-TDDB-test (Constant Current Stress Time Dependence Dielectric Breakdown), var typiskt 15 C/cm², vilket är jämförbart med värdet för kiselkomponenter.

Fig 9. Simulering av hur drain-source-bias påverkar fördelningen av det elektriska fältet vid 600 V och en gate-source-spänning på 0 V

Negativ gate-bias hos kommersiella SiC-MOSFETar är begränsad till -6 V. Det beror på att kontinuerligt negativ gate-bias orsakar en negativ förändring av tröskelspänningen, troligen orsakat av hålfällor i gate-oxiden eller MOS-gränssnittet. Men ändringstakten hos tröskelspänningen hos SiC trench-MOSFETar vid test med en negativ bias Vgs = -18 V efter 3 000 timmar uppgick till blott 5 procent.

Fig 10. Elektriska fältstyrkan för enkel och dubbel trench-struktur

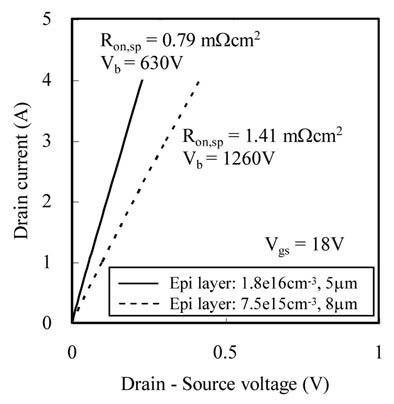

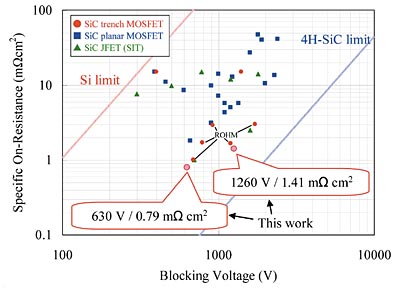

Fig 11 visar två olika slags Id/Vds-karakteristika för trench-MOSFETar som använder olika episkikt: 1,816 cm-3/5 µm och 7,515 cm-3/7 µm. Brickstorleken är samma, 2,56 mm², och de aktiva ytorna är 1,422 mm². Ron hos dessa uppskattades till 0,79 resp 1,41 milliohm×cm² vid Id = 1 A. Blockeringsspänningen hos dessa var 690 resp 1 200 V vid Id = 100 µA. Fig 12 jämför prestanda hos olika 4H-SiC-switchkomponenter. ROHM har kunnat uppnå låg till-resistans och samtidigt bibehålla hög tillförlitlighet hos gate-oxiden.

Fig 11. Två olika slags Id/Vds-karakteristika visas här för trench-MOSFETar som använder olika episkikt: 1,816 cm-3/5 µm och 7,515 cm-3/7 µm. Brickstorleken är samma, 2,56 mm², och de aktiva ytorna är 1,422 mm². Ron hos dessa uppskattades till 0,79 resp 1,41 milliohm×cm² vid Id = 1 A. Blockeringsspänningen hos dessa var 690 resp 1 200 V vid Id = 100 µA.

Ingen degradering

ROHMs nyutvecklade SiC-planar-MOSFETar har undertryckt degraderingen av parasitiska PN-junctiondioder när framåtströmmar tränger igenom. SiC-Schottkydioder med trench-struktur har framgångsrikt uppvisar ultralåga spänningsfall, men ändå bibehållit låga läckströmmar. SiC-MOSFETar med dubbel trench-struktur har givit ultralåg till-resistans med förbättrad tillförlitlighet hos gate-oxiden.

Fig 12. Diagrammet visar prestanda för olika 4H-SiC-switchkomponenter. ROHM har kunnat uppnå låg till-resistans och samtidigt bibehålla hög tillförlitlighet hos gate-oxiden.

Masanori Tanimura, ROHM

Filed under: Halvledarteknik