20 nm ger Xilinx ASIC-prestanda

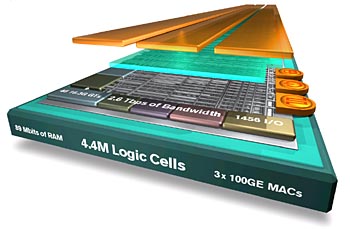

I november fick Xilinx de första 20 nm-proverna från TSMC och nu är det dags att leverera komponenter till användare. Den nya Virtex UltraSCALE-generationen innehåller FPGA-komponenter med upp till 4 407 logikceller. Det motsvarar upp till 50 miljoner ekvivalenta ASIC-grindar.

– Men det är långt ifrån allt vi har gjort, säger Giles Peckham, marknadschef för Europa hos Xilinx. Den nya generationen Kintex-FPGAer har fått en ännu mer dramatisk prestandauppdatering och då talar vi inte bara om nästan tre gånger så mycket programmerbar logik. DSP-prestanda ökar också med nästan tre gånger, med fler och bredare multiplikatorer.

Att Xilinx har valt att öka Kintex-familjens prestanda såpass kraftigt beror bland annat på Kintex allt mer kommit att användas inom signalbehandlingstillämpningar.

– Tidigare såg man Kintex mera som en lillebror till Virtex, med lite mindre av allt. Men efter hand ökade behoven av DSP-prestanda och vi tog beslutet att göra Kintex till det självklara valet i DSP-sammanhang. Den största versionen av Kintex har nu faktiskt nästan dubbelt så många DSP-block som den största Virtex-versionen.

– Virtex används framför allt i tillämpningar med mycket hög bandbredd och vi ökar bandbredden för varje generation. Det finns nu upp till 104 tranceivers per komponent och vi har ökat den maximala hastigheten till 32,75 Gbit/s per tranceiver. Vi har också lagt in fler snabba seriella gränssnitt. Idag finns som mest sju stycken 100 Gbit Ethernet-block och nio 150 Gbit Interlakenblock.

– Något som inte är alldeles uppenbart är att FPGA-areorna har samma prestanda i Kintex och Virtex. De bägge familjerna är byggda på samma sätt och i samma process och klockas med samma hastighet. Däremot skiljer typen av I/O-gränssnitt och hastigheten på gränssnitten. Och så förstås storlek och pris.

Virtex UltraSCALE är också i fortsättningen störst, mest avancerad och förstås dyrast, medan Kintex ligger lite lägre i pris. Men ingen av budgetalternativen, som Arctix, kommer att tillverkas i 20 nm.

– Idag ser vi inte några kostnadsfördelar i att skala från 28 nm till 20 och 16 nm. De nya processerna kräver mera avancerade och dyrare masker och blir därför dyrare också vid samma storlek. Därför kommer vi att fortsätta att tillverka Arctix-familjen i 28 nm-teknologi och vi har inga planer att skala den familjen till 20 nm.

Verktygen blir allt viktigare

Med FPGA-areor motsvarande upp till 50 miljoner ASIC-grindar ställs förstås mycket stora krav på konstruktionsverktygen. Xilinx har ägnat mycket tid åt att ta fram verktyg och konstruktionsmetoder som kan automatisera layoutarbetet och snabba upp tiden från konstruktion till färdig implementering.

– Idag är det routing-fördröjningen som dominerar och det är oerhört viktigt att packa CLB-blocken på ett optimalt sätt. Därför har vi gjort om routing-arkitekturen, dubblat routing-resurserna och optimerat det hela tillsammans med routingverktyget. Resultatet är att konstruktörerna kan nå upp till 90 procents användning av FPGA-resurserna utan prestandaförsämringar.

Tillsammans med de nya verktygen är det möjligt att korta ner konstruktionscyklerna kraftigt och minska antalet iterationer. Förbättringarna finns i alla de olika stegen, från verifiering till routning.

– Vi har till exempel lyckats att snabba upp C++-verifieringen med en faktor 15 och implementeringen med en faktor fyra. Totalt sett ger den nya metodiken möjligheter att korta ner tiden fram till färdigt resultat från månader till veckor.

Filed under: Utländsk Teknik