Högre utbyte med noggrannare korrektion

Med en rad korrektioner och optimeringar har halvledartillverkarna lyckats att nå förvånansvärt högt produktionsutbyte, också i de senaste geometrierna. Men ännu så länge har man inte tagit hänsyn till variationerna över arean på en wafer. Philippe Morey-Chaisemartin och Eric Beisser från det franska EDA-företaget Xyalis beskriver här en metodik som gör det möjligt att kompensera också för de variationerna.

En del produktionssteg vid halvledartillvekning leder till processvariationer på wafernivå som inte går att bortse från. Vi har framför allt kemisk-mekanisk planarisering, CMP, som är en icke-homogen process och där man kan se variationer i tjocklek beroende på hur långt från centrum ett visst chip är. Variationerna inverkar sedan på det individuella chipets prestanda och dessutom på det slutliga processutbytet. Den här effekten kan förstärkas av det faktum att tjockleksvariationer på bearbetade wafers ger problem med fokusering i senare fotolitografiska steg.

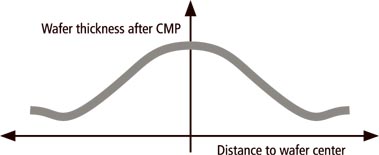

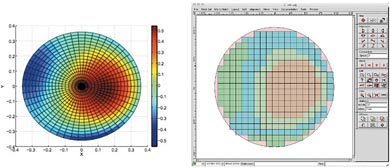

Fig 1. Typisk tjockleksvariation.

Normalt sett minimerar man problemen med varierande tjocklek på grund av CMP genom att lägga in "dummies". Men de korrigeringarna baseras bara på modeller som använder genomsnittliga värden.

I den här artikeln föreslår vi en metodik som gör det möjligt att göra olika optimeringar på olika delar av en wafer. Metodiken drar nytta av en befintlig teknik som kallas "Multi Layer Reticles", och kräver därför inga nya investeringar i utrustning.

Introduktion

I alla klassiska metoder för att förbättra produktionsutbytet vid planarisering (CMP) används "dummy shapes", alltså mönster som inte har med konstruktionen att göra. De läggs in i originalkonstruktionen beroende på genomsnittliga processparametrar, som i sin tur baseras på variationen mellan olika chip på wafern. Förutom variationen mellan de individuella chipen har många studier också pekat på variationerna på wafernivå.

Dessa processvariationer kan ha stor inverkan på komponentprestanda och kan leda till icke-fungerande chip eller prestanda som ligger utanför specifikationen. Problemet blir allt mera kritiskt i takt med att teknologinoderna utvecklas.

Förhoppningsvis är CMP-processvariationerna över en wafer ganska förutsägbara. Här skall vi beskriva hur man kan göra för att förbättra det övergripande processutbytet genom att justera de klasiska layoutoptimeringarna. DFM-optimeringarna görs med hänsyn inte bara till de genomsnittliga processparametrarna, utan också till en extra parameter, som är avståndet från chipet till waferns centrum.

Den här optimeringen kan användas antingen för att optimera "dummy insertion" eller för att korrigera optisk proximitet. I det första fallet är målet att minska variationerna i tjocklek över wafern. I det andra fallet är målet att ta hänsyn till de existerande tjockleksvariationerna i OPC-modellen. I bägge fallen görs varianter av originallayouten för olika positioner på samma mask.

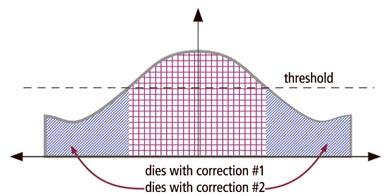

Fig 2. Två olika korrektioner.

I den här artikeln kommer vi att analysera tjockleksvariationerna på wafers med standardprocesser och se på deras inverkan på processutbytet. Vi kommer att föreslå en metodik som justerar modellerna för "dummy insertion" och OPC, baserad på ett chips position på en wafer. Vi kommer också att ge en detaljerad analys av slutkostnaden. Slutligen kommer vi dessutom att beskriva en procedur för att automatiskt generera en "stegningsplan" för att hantera de olika optimerade fälten på wafern.

Den nya optimeringsmetodik som vi föreslår kräver inga nya utrustningar och begränsade extrakostnader. Detta eftersom den baseras på en kombination av MLR, modellbaserad CMP och modellbaserad OPC, som alla är klassiska masktekniker som används standardmässigt idag.

Olika regioner

Processvariationer kan delas upp i variationer mellan chip (inter-die) och generella variationer över hela wafern (intra-die). De variationer på wafernivå som uppstår på grund av CMP-processer är lätta att mäta. Fig 1 visar en statistisk analys av tjockleksvariationen som uppstår på grund av CMP.

I klassiska konstruktionsflöden läggs samma "dummy patterns" in på alla chip på en wafer. De här mönstren skall minimera tjockleksvariationen efter CMP och baseras på genomsnittliga mätvärden över hela wafern.

Procedurerna för att lägga in "dummy patterns" är oftast modellbaserade. Modellerna tar hänsyn till designspecifika parametrar, som t ex mönstertäthet (pattern density) och fysiska parametrar, som t ex "slurry characteristics", alltså egenskaper hos den slipvätska som används för den mekaniska slipningen. Vi vill också lägga till en ytterligare parameter, baserad på avståndet från ett individuellt chip till centrum av en wafer.

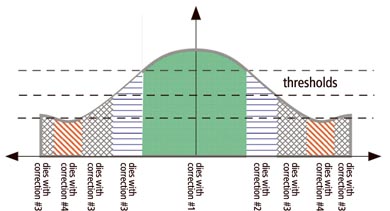

Fig 3. Fyra olika korrektioner.

Naturligtvis kan man inte generera individuella "dummy patterns" för varje separat chip, men vi kan definiera olika regioner, baserade på tröskelvärden av en uppskattad tjockleksvariation. De chip som tillhör en viss region på wafern kommer att processas med parametrar anpassade för den specifika regionen. Med bara ett enda tröskelvärde kan vi definiera två regioner på wafern, som framgår av fig 2.

Om vi i stället har tre olika tröskelvärden kan vi definiera fem olika regioner, som framgår av fig 3. Ju fler tröskelvärden som definieras, desto mer noggrann kommer CMP-modellen att bli. Men det kan också leda till en dramatisk ökning av maskkostnaden och en mera komplex fotolitografisk process.

Upp till fyra fält

Ett klassiskt sätt för att reducera maskkostnaden är att använda samma "reticle" (mask för mönsterprojektion i en stepper) för olika lager. Masken kan delas i två eller fyra fält och varje fält innehåller mönstret för ett individuellt lager.

Vi föreslår här en teknik där de olika fälten i stället används för olika versioner av samma lager. Varje fält är då optimerat för en speciell region, med "dummy patterns" som anpassats för den individuella regionen. Med en sådan teknik kan vi hålla kostnaden för en komplett uppsättning masker konstant. Den ökade kostnaden ligger i den längre exponeringstiden i steppern, eftersom varje exponering bara täcker hälften eller en fjärdedel av den maximala arean. Steppern måste alltså göra dubbelt så många eller fyra gånger så många exponeringar.

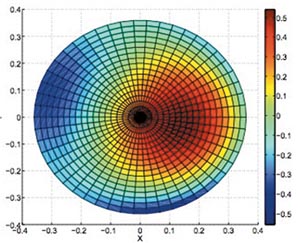

Fig 4. Icke-symmetrisk processvariation på wafernivå.

Den här metoden kan också användas för att rätta till fokuseringsproblem beroende på wafertjockleken. I det här fallet kan OPC-modellen ta hänsyn till tjockleksparametern och göra olika korrektion (OPC) på olika regioner på wafern. Det kan också vara möjligt att justera OPC "dynamiskt". Det skulle i så fall betyda att olika wafers kan ha olika ställen där en viss optimerad version passar bäst.

Tjockleksvariationen är kanske inte symmetrisk som förväntat, utan i stället distribuerad, till exempel på det sätt som fig 4 visar. Då kan platsen där de olika regionerna appliceras ändras.

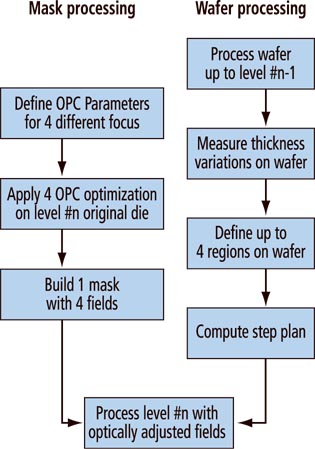

Fig 5. Processflöde med dynamisk OPC-optimering.

Det här kräver förstås tjockleksmätning av varje individuell wafer och leder till en mycket mer komplicerad process. Men, i de fall när varje parameter måste justeras perfekt för att nå acceptabelt produktionsutbyte kan tekniken vara en lösning. Fig 5 visar ett tänkt processflöde med dynamisk OPC-optimering.

Optimering av kostnader

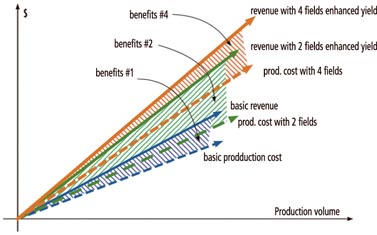

Den övergripande kostnaden för den här typen av optimering består å ena sidan av extrakostnaden för själva halvledarproduktionen och å andra sidan fördelarna i form av förbättrat produktionsutbyte (yield). Extrakostnaden i produktionssteget ligger framför allt i de mindre fälten och ökade antalet exponeringar som blir resultatet av att använda tekniken för "Multi Layer Reticles". Fig 6 visar en detaljerad kostnadsanalys och ger en fingervisning för när en tvåfälts- eller fyrfälts reticle bör väljas.

Fig 6. Ekonomisk vinst i förhållande till produktionskostnad.

Valet mellan inga extra fält, två fält eller fyra fält kan göras individuellt för varje lager. Valet beror framför allt de förväntade processvariationerna på wafernivå och deras påverkan på komponentprestanda.

Stegningsplan

Som beskrivits tidigare skall de olika fälten på en reticle kopplas till de olika regionerna på wafern utifrån de olika optimeringskriteria som används. Wafermappen är en homogen array av chip.

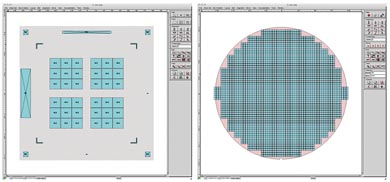

Fig 7. MLR-floor plan och wafermap.

Att använda olika fält på samma reticle för att exponera olika mönster är ett vanligt sätt för att exponera moduler för processkontroll på wafern. Att driva steppern (eller scannern) till att exponera antingen fält som korresponderar till det grundläggande chipet eller processkontrollfält görs med hjälp av en stegningsplan (step plan). I vårt fall kan stegningsplanen, alltså beskrivningen av var på wafern de individuella fälten skall exponeras, genereras utifrån de tröskelnivåer som har genererats.

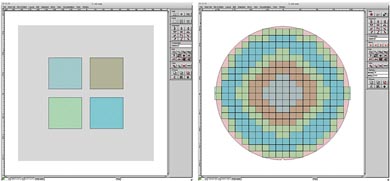

Fig 8. Stegningsplan relaterad till olika fält.

Som vi nämnt tidigare kan en stegningsplan tas fram en gång för alla, utifrån den uppskattade genomsnittliga processvariationen över wafern. Alternativt kan den justeras utifrån de verkliga variationerna som mäts under processen. Fig 9 visar en stegningsplan som justerats under waferprocessen för att exakt motsvara de verkliga tjockleksvariationerna.

Fig 9. Dynamiskt justerad stegningsplan.

I bägge fallen (fig 8 och fig 9) kommer fotolitografisteget att förlängas, beroende på att varje exponering bara täcker hälften eller en fjärdedel, jämfört med om hela masken används. Men, om de olika instanserna ligger på samma reticle, kan hela processen göras med en enda mask.

Philippe Morey-Chaisemartin. Eric Beisser, Xyalis

Referenser:

* Frank Fox Anantha P. Chandrakasan, William J. Bowhill. Design of High-Performance Microprocessor Circuits, chapter Models of process variations in device and interconnect, sid 98–115. Nummer 6. Wiley-IEEE Press, 2000.

* Lerong Cheng, Puneet Gupta, Costas Spanos, Kun Qian, och Lei He. Physically justifiable dielevel modeling of spatial variation in view of systematic across wafer variability. Proceedings of the 46th Annual Design Automation Conference, DAC ’09, sid 104–109, New York, NY, USA, 2009. ACM.

* G. Gielen, P. De Wit, E. Maricau, J. Loeckx, J. Martín-Martínez, B. Kaczer, G. Groeseneken, Rodríguez, och M. Nafría. Emerging yield and reliability challenges in nanometer CMOS technologies. Proceedings of the conference on Design, automation and test in Europe, DATE ’08, sid 1322–1327, New York, NY, USA, 2008. ACM.

* Puneet Gupta och Andrew B. Kahng. Manufacturing-aware physical design. Proceedings of the 2003 IEEE/ACM international conference on Computer-aided design, ICCAD ’03, sid 681–, Washington, DC, USA, 2003. IEEE Computer Society.

* Andrew B. Kahng, Swamy Muddu, and Puneet Sharma. Defocus-aware leakage estimation and control. Proceedings of the 2005 international symposium on Low power electronics and design, ISLPED ’05, sid 263–268, New York, NY, USA, 2005. ACM.

* Dornfeld David A Luo Jianfeng. Wafer-scale CMP modeling of with-in wafer non-uniformity.

Filed under: EDA