Bredbandig RF-transceiver

ADRV9026 från Analog Devices är konstruerad för att passa i multistandard makrocells basstationer för 3G/4G/5G, massiv MIMO (M-MIMO) och system med små celler. Kretsen har fyra kanaler som kan arbeta med TDD eller FDD (tids- eller frekvensmultiplex).

ADRV9026 utmärker sig av låg effekt och litet format. Den är kapslad i 14×14 mm ”chip scale BGA” med 289 anslutningar. Centerfrekvensen varierar mellan 650 och 6000 MHz. Maximal bandbredd är 200 MHz i sändare/mottagare.

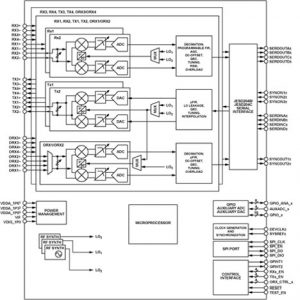

ADRV9026 är en högintegrerad, sändtagare med fyra oberoende kontrollerade sändare, dedikerade observationsmottagaringångar för övervakning av varje sändarkanal, fyra separat styrda mottagare, integrerade synthesizers och digitala signalbehandlingsfunktioner som ger en komplett sändtagarlösning.

Enheten ger de prestanda som krävs av applikationer för mobilinfrastruktur, till exempel små basstationsradioer, makro 3G/4G/ 5G-system och massiva multipla in/multipla basstationer (MIMO).

Mottagarsubsystemet består av fyra separata direktkonverterande mottagare med stort dynamik och hög bandbredd.

De fyra separata sändarna använder en direktomvandlingsmodulator med lågbrusdrift och energiförbrukning. Enheten innehåller också två bredbandiga, tidsdelade mottagare med två ingångar vardera för att övervaka sändarutgångar.

Det kompletta sändtagarsundersystemet inkluderar automatisk och manuell dämpningskontroll, DC-offsetkorrigering, kvadraturfelskorrigering (QEC) och digital filtrering, vilket eliminerar behovet av dessa funktioner i de digitala basbanden.

Andra hjälpfunktioner såsom A/D-omvandlare, D/A-omvandlare och generella in-/utgångar (GPIO) som ger en rad digitala styralternativ är också integrerade.

För att uppnå höga RF-prestanda inkluderar sändtagaren fem helt integrerade faslåsta slingor (PLL). Två PLLer har bråktalsdelning i RF-syntesoscillatorn för sändar- och mottagarsignalvägarna.

En tredje integrerad PLL stöder ett oberoende lokalt oscillatorläge för observationsmottagaren.

En fjärde PLL genererar de klockor som behövs för omvandlarna och digitala kretsar, och en femte PLL tillhandahåller klockan för det seriella datagränssnittet.

En multichip-synkroniseringsmekanism synkroniserar fasen för alla lokaloscillatorer och basbandsklockor mellan flera ADRV9026-chips. Alla spänningsstyrda oscillatorer (VCOer) och slingfilterkomponenter är integrerade och justerbara genom det digitala styrgränssnittet.

Det seriella datagränssnittet består av fyra serielliseringsfält och fyra deserialiseringsfält. Gränssnittet stöder både JESD204B- och JESD204C-standarder och fungerar med datahastigheter upp till 16 Gbit/s. Gränssnittet stöder också ett läge för interfoliering, vilket ger lägre bandbredd. Både fasta och flytande format stöds. Flyttalsformatet gör att intern automatisk förstärkningskontroll (AGC) kan vara osynlig för demodulatorenheten.

Blockschema över ADRV9026

Filed under: Utländsk Teknik