Vad innebär industriell NAND

Det finns stora skillnader mellan olika typer av flashminnen och i embeddedtillämpningar är det är speciellt viktigt att inse vilka de är. Alex Tseng från ATP Electronics gör här en genomgång av de olika teknologierna och vad man bör tänka på.

Översvämningarna i Thailand förra året ledde till brist på kritiska komponenter för hårddiskar. Resultatet blev hårddiskbrist och snabbt ökande priser och det ledde i sin tur till ökande efterfrågan på flashbaserade SSD-diskar. Många som väntat med att gå över till SSD tog nu steget, inte minst i industritillämpningar.

Vad är NAND?

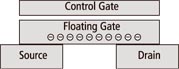

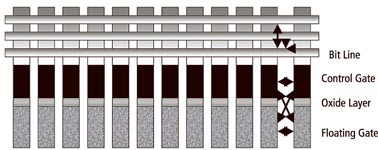

Det minsta byggblocket i en NAND-cell består av en transistor, en "control gate" och en "floating gate" för att lagra elektroner. Fig 1 visar grundstrukturen hos en flashcell.

Ett spänningsfält bildas av spänningsskillnaden mellan drain och source. Detta fält gör det möjligt för elektronerna att flöda mellan cellens source och drain.

Fig 1. Flashcell.

Ytterligare ett fält skapas genom att en spänning läggs på cellens control gate (styre). Det medför att en del av elektronerna attraheras och lagras i cellens floating gate. Elektronerna kommer att laddas till olika spänningar och bilda ett "band". Den lägre gränsen kallas tröskelspänningen. Genom att mäta spänningen i en cell och jämföra den med tröskelspänningen kan man avgöra om en cell är programmerad eller raderad. Det går också att ha mer än en nivå på tröskelspänningen och det leder oss in på skillnaden mellan SLC och MLC.

SLC, MLC OCH TLC

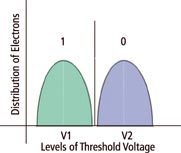

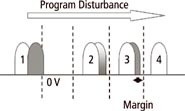

Single Level Cell, SLC, är en väldefinierad NAND-struktur. Cellen har bara en tröskelnivå, som namnet antyder. När spänningsnivån är högre än tröskelnivån definieras cellen som programmerad eller "1". När spänningsnivån går under tröskelnivån definieras cellen som raderad eller "0". En SLC-struktur har stor feltolerans, vilket framgår av fig 2.

I MLC-teknologi (Multiple Level Cell) känner man av flera olika spänningsnivåer hos cellen och kan på det sättet låta varje cell representera flera bit. tekniken kräver mycket noggrann kontroll av spänningen i cellen. Fig 2 visar hur olika tröskelspänningar definieras i en MLC-cell.

Fig 2. Tröskelspänning i en SLC-cell.

Genom att känna av fyra nivåer kommer varje cell att motsvara två bit. Konstruktionen måste vara mycket känslig för att känna av de mycket små spänningsskillnader som motsvarar olika data. På samma sätt blir proceduren att ladda cellen till rätt nivå mycket känsligare.

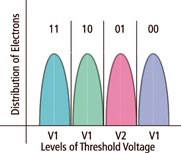

Tar man tekniken ytterligare ett steg längre går det att lagra tre bit per cell genom att skilja mellan åtta nivåer. MLC och TLC kan alltså lagra två, respektive tre gånger så mycket data med samma antal flashceller. Flashminnen med MLC- och TLC-celler är därför betydligt billigare än motsvarande minnen med SLC-celler.

En variant av MLC kallas "enterprise MLC" eller eMLC. eMLC är framtagen för att klara fler programmerings/raderings-cykler (P/E-cykler) än vad normala MLC-celler klarar. eMLC använder olika tekniker för att öka antalet P/E-cykler. Den stora skillnaden ligger i de smalare "banden", som i sin tur kräver noggrannare programmering.

Fler P/E-cykler tenderar att flytta "banden" mot den övre eller nedre gränsen, något som kallas "program disturbance". eMLC-konstruktionens smalare band minskar sannolikheten för läsfel och ökar på det sättet antal P/E-cykler. Men samtidigt tenderar eMLC-konstruktionen med sina smalare band att lättare tappa laddade elektroner över tiden. Det gör i sin tur att lagringstiden blir kortare. "Data retention" är förmågan hos ett NAND-minne att behålla lagrade data en viss tid. eMLC ökar antalet P/E-cykler, men minskar lagringstiden.

Fig 3. Tröskelspänningar i en MLC-cell

En teknik som används flitigt i eMLC-minnen är felkorrigering, ECC. ECC-logiken korrigerar datafel som uppträder på grund av ökat antal P/E-cykler. Men ECC gör också minnet långsammare. eMLC ger alltså ökat antal programmeringscykler till priset av kortare lagringstid och sämre prestanda.

Problem med MLC och TLC

I en idealisk konstruktion borde spänningsdistributionen inom området definierat av en tröskelspänning kunna styras mycket noggrant. Men, spänningsdistributionen ändras när cellerna krymper vid nya komponentgenerationer. Cellerna kommer närmare varandra och det ökar störningarna via elektrisk överhörning.

Det går att hitta överhörning mellan "floating gates", "control gates" och bitledningar. Resultatet är ett brus som orsakar "Program Disturbances", PD.

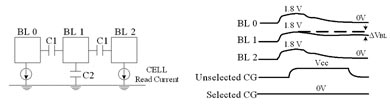

"Bit Line coupling noise" kan användas för att demonstrera problemet med överhörning. Bitledningen är en metalledare i en cell som leder ström till source och drain. Fig 4 visar kopplingskapacitansen C1 och störningen på bitledningen BL1, orsakad av BL0 och BL2. I en läsoperation ger strömmarna från BL0 och BL2 en elektrisk störning på BL1 med spänningsskillnaden deltaVBL. En tillräcklig spänningsskillnad kan resultera i ett fel. MLC och TLC arbetar med mycket små spänningsskillnader och är därför extra känsliga.

Programmeringsproblem

Elektrisk överhörning i en MLC-cell kan leda till "program disturbance", PD, vilket ändrar spänningsskillnaderna hos de elektroner som lagras i "floating gate". Varje programmering eller skrivning kan ge en störning till övriga existerande tillstånd. fig 5 visar ett "worst case"-scenario där de återstående tre tillstånden störs när ett fjärde tillstånd skrivs in. Banden för varje tillstånd blir bredare eller skiftar position.

Fig 4. Brus på grund av överhörning i bitledningarna.

En lösning är att programmera elektronerna i alla omgivande celler så att spänningsdistributionen minskar. På det sättet kan man kompensera för PD. Det kan samtidigt försämra prestanda, på grund av att så mycket omprogrammering kommer att göras i bakgrunden. Det är också uppenbart att en TLC-cell med mer än fyra bit kommer att ha en ännu mera sofistikerad skrivprocess för att reducera problemen med PD. Fig 6 visar hur problem orsakade av överhörning kan observeras mellan olika delar av celler.

ytterligare en faktor att ta hänsyn till är den längre accesstiden för MLC och TLC jämfört med SLC. Längre accesstid ger längre exponeringstid för PD.

Industriell NAND

En industriell NAND-produkt måste ha hög tillförlitlighet i svåra omgivningsförhållanden och dessutom klara ett stort temperaturområde. Här är det viktigt att konstruktörer tar hänsyn till de nackdelar som MLC- och TLC-produkter har i förhållande till SLC-minnen. Man bör i första hand se SLC-produkter som "riktiga" industriklassade minnen. Här är några viktiga parametrar.

Tillräckligt många p/e-cykler

En del industridatorer kräver ständig uppdatering av bootkoder eller andra parametrar. När ett MLC-minne närmar sig sitt maximala antal P/E-cykler riskerar systemen att låsa sig. SLC-minnen har mer än tio gånger så många P/E-cykler, bland annat beroende på att varje cell i ett MLC-minne innehåller fler bit och därför accessas oftare. Den stora skillnaden i antal cykler kompenserar det högre priset för SLC i industrisammanhang.

Lagringstid

Eftersom ett SLC-minne har bredare band och större tolerans är det också lättare att acceptera att spänningen förändras över tiden. Det innebär att SLC-produkter har ca tio gånger längre lagringstid än MLC-produkter.

Accesstid för läsning

Läshastigheten används alltid som jämförelse mellan olika typer av minnen. Vissa typer av filer, till exempel operativsystemsfiler, kan läsas miljontals gånger utan att ändras. Tillämpningar som 3D-TV kräver mycket högre läshastigheter än "vanlig" TV. Därför är läshastigheten en viktig parameter.

Fig 5. Störningar kan orsaka felläsningar.

SLC-minnen är mycket snabbare än MLC, eftersom MLC och TLC kräver komplexa läs- och skrivalgoritmer. SLC ger också betydligt snabbare tillgång till godtyckliga sidor.

Accesstid för skrivning

Tidigare var inte kraven på snabb programmering för MP3-spelare eller digitalkameror särskilt stora och MLC-produkter dög bra. Men med allt mer HD-video ökar också kraven på snabb programmering.

Fig 6. Överhörning mellan närliggande cell-komponenter.

Idag använder SD Association klass 2/4/6/10 för att representera motsvarande hastigheter i Mbyte/s för olika användningsområden. Att skriva en 10 Gbyte stor fil med ett minne som klarar 2 Mbyte/s ger en skrivtid på ca 1,5 timmar. Det är alldeles för mycket för att kopiera en HD-film.

För snabb programmering är SLC ett självklart val. Ett SLC-baserat SSD-minne innehåller till exempel många SLC-komponenter med många skrivkanaler. Ett minne med 20 SLC-chip med vardera 10 Mbyte/s skrivhastighet kan nå 200 Mbyte/s.

Större temperaturområde

industriprodukter måste ofta arbeta i ett stort temperaturområde. SLC har större toleranser än MLC och klarar därför större variationer.

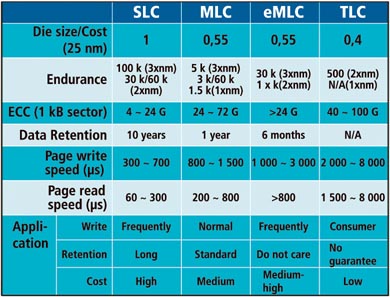

Fig 7 summerar de olika egenskaperna hos SLC, MLC, eMLC och TLC. Allmänt sett har SLC bättre data med mindre behov av ECC. Däremot är priset högre. För att nå ett lägre pris offrar övriga tekniker prestanda, antal cykler eller lagringstid på olika sätt.

Fig 7. Prestanda för olika flasharkitekturer.

Priset är naturligtvis viktigt också i embeddedsammanhang, men normalt sett bör tillförlitlighet och prestanda göra att valet väger över till fördel för SLC.

Framtida utmaningar

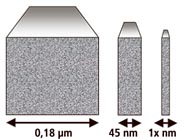

En intressant parameter är storleken på en cells floating gate. Den minskar med varje ny generation och det ger nya utmaningar.

En floating gate kan betraktas som en "svart låda" som lagrar laddning. Lagringskapaciteten är proportionell mot FG-kanalens area. Vi kan anta att lådans area är en fjärdedel när FG-kanalens bredd/längd halveras.

Efter en lång tids datalagring kommer laddningarna att minska och vi får problem med datalagringen. Fortfarande specificerar minnestillverkarna tio års lagring, men för varje ny generation blir det allt svårare att klara den gränsen. Tittar vi till exempel på tvärsnittsarean hos en 45 nm-cell i fig 8 ser vi att den bara är en sextondel av den hos en 180 nm-cell. Det innebär motsvarande mindre mängd laddning. Volymen blir bara 1/36 av originalstorleken och det krävs stora modifieringar för att kunna lagra lika mycket laddning. Ett sätt kan vara att öka det elektriska fältet. Ett annat kan vara att använda nya material.

Fig 8. Nyare flashminnen "rymmer" mindre laddning.

Men det enklaste är ändå att minska den garanterade lagringstiden och vi ser allt fler produkter som garanterar tre år i stället för tio. Detta är något att hålla ögonen på.

Alex Tseng, product Management Director, ATP Electronics

Filed under: Embedded