Staplade nanotrådar som styren i CMOS

Världens första CMOS med vertikalt staplade styren (gates) i form av en helt omsluten kisel-nanotråd (vertically stacked gate-all-around, GAA) demonstrerades av IMEC på årets IEEE IEDM konferens, Electron Devices Meeting 2016. De lyckade resultaten bådar gott för FinFET i framtida teknologinoder.

Konferensen är ett världsledande forsknings- och innovationsnav för nanoelektronik och digital teknik. På årets IMEC rapporterade man för första gången om integrerationen av CMOS som byggts med vertikalt staplade gate-all-around (GAA) kiselnanotråds MOSFET. En nyckelfaktor vid integrationen är en dubbelfungerande metall-gate som möjliggör matchade tröskelspänningar för MOSFET av n- och p-typ.

Man har studerat ESD-tåligheten i den nya arkitekturen och föreslår att ESD-skyddsdioder.

GAA nanotråds transistorer är lovande kandidater för FinFET i 7 nm och kommande tekniknoder. Tack vare att man har kontroll av elektrostatiska egenskaper passar de för skalning av CMOS.

Eftersom de är horisontellt konfigurerade utgör de en naturlig förlängning av dagens ordinära FinFET-teknik.

I den här konfigurationen, kan drivströmmen för ett givet fotavtryck maximeras genom att vertikalt stapla flera horisontella nanotrådar. Tidigare i år visade IMEC-forskare GAA FET som bygger på vertikalt staplade Si-nanotrådar med 8 nm diameter. Dessa komponenter uppvisade utmärkt kontroll av elektrostatiska egenskaper, men tillverkningen av n- och p-FET skedde då separat.

Matchade tröskelspänningar

IMEC rapporterar nu om CMOS där man integrerat vertikalt staplade GAA Si nanowire n- och p-MOSFET med matchade tröskelspänningar. Viktigt för denna integration är att man åstadkommit dubbelfunktionella metallgrindar med individuellt ställda tröskelspänningar av n- och p-FET.

Det går till så att p-typens metall (PWFM) deponeras i gate-diken för alla kretsar, följt av selektiv etsning av PWFM ner till HfO2 från N-FET-arna och efterföljande deposition metall för n-typens metall. Genom att se över matchade tröskelspänningar (VT, SAT = 0,35 V) för nMOS- och PMOS-kretsar kan man säkra dubbla arbetsfunktioner hos det integrerade metallsystemet.

Effekterna av denna nya kretsarkitektur med avseende på interna ESD-prestanda undersöktes även. ESD-skydd med två olika dioder har föreslagits: Dels en diod med grind-struktur (gated diod), dels en diod med grund dikesisolering, ”shallow-trench isolation defined diode” (STI-diod). STI-dioden visade sig ge bättre ESD-skydd och uppvisade ett utmärkt förhållande mellan felström (It2) och parasitkapacitans (C).

Mätningar och TCAD-simuleringar av GAA-nanotrådsbaserade dioder visar också ESD-prestanda i paritet med bulk FinFET-dioder.

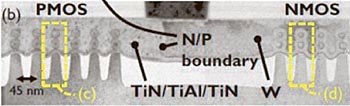

(a) SEM-bild uppifrån efter PWFM-etsning av n-FET, och (b) – (d) tvärsnitts TEM-bilder av p- och n-FET i slutet av processen (LG = 30 nm).

(a) SEM-bild uppifrån efter PWFM-etsning av n-FET, och (b) – (d) tvärsnitts TEM-bilder av p- och n-FET i slutet av processen (LG = 30 nm).

Filed under: SvenskTeknik