Matcha ESD-skydd mot processgeometri

Avancerade CMOS-processteknologier gör att kretskonstruktörer kan konstruera högpresterande enheter men de kräver också extra ESD-skydd på kretskorten för att garantera produktens tillförlitlighet.Robert Ashton Ph D, sr protection & compliance specialist, ON Semiconductor, beskriver här några teknologitrender för integrerade kretsar.

Framstegen inom CMOS-teknologin har gjort det möjligt för halvledartillverkare att tillverka integrerade kretsar med allt mindre geometrier.

Dessa mindre geometrier för integrerade kretsar ger många fördelar. Mindre geometrier gör att fler funktioner får plats på mindre yta och resulterar i integrerade kretsar med fler funktioner på mindre kiselyta och till lägre pris. CMOS-transistorer med mindre geometrier har också bättre prestanda. Resultatet är en win-win-win-situation, med fler funktioner och bättre prestanda till lägre kostnad.

CMOS-processgeometrier har minskat dramatiskt. Mogna processer på 0,18 µm eller 0,13 µm kan vara kostnadseffektiva för kundanpassade ASIC-projekt med blandade analoga och digitala funktioner. Toppmoderna digitala kretsar har geometrier på 45 nm, 32 nm och till och med 28 nm.

En sidoeffekt av de mindre geometrierna är kravet på lägre matningsspänningar. Sänker man inte matningsspänningarna kan det leda till fel i gateoxiden och ge andra tillförlitlighetsproblem som transistoråldring.

Lägre spänningar har både positiva och negativa sidor:

* På den positiva sidan medför lägre matningsspänningar lägre effektförbrukning, vilket är en stor fördel i dagens populära batteriförsedda, portabla enheter.

* På den negativa sidan medför lägre matningsspänningar några av elektronikkonstruktioners utmaningar som minskat dynamiskt omfång och lägre signal/brusförhållande. Dessutom har elektriska påfrestningar som elektrostatiska urladdningar (ESD), som elektroniska enheter som datorer och mobiltelefoner utsätts för, inte minskat vare sig i spänning eller i ström när teknologin för integrerade kretsar gått framåt.

Undvik ESD-fel

Resultatet är att lägre ESD-nivåer nu kan skada moderna integrerade kretsar. Det leder till konsekvenser för hur elektroniksystem konstrueras för att klara ESD. För inse dessa konsekvenser är det nödvändigt att förstå hur ESD-skydd används i kretskonstruktioner.

Principerna för ESD-konstruktion är likartade på kretsnivå och på systemnivå så vi börjar med att utreda skydd på kretsnivå och går vidare till systemnivå. Vi kommer också att lära oss hur ESD-skydd på kortnivå och lämplig kortkonstruktion är viktiga verktyg för ESD-skydd på systemnivå.

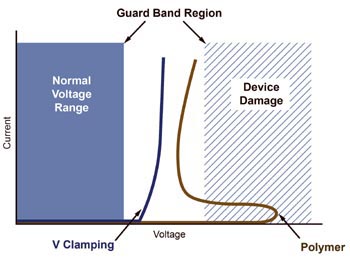

Alla elektroniska komponenter och kretsar har ett specificerat arbetsspänningsområde och ett säkerhetsområde, så som visas i fig 1. Spänning över detta område leder till skador på kretsen. Då avancerade processteknologier kräver lägre arbetsspänningar medför detta att säkerhetsområdet krymper.

Komponenter för ESD-skydd används för att se till att spänningen håller sig inom skyddsområdet vid ESD-påfrestningar. Då skyddsområdet krymper behövs komponenter för ESD-skydd med lägre ledningsresistans så att spänningen kan hålla sig inom skyddsområdet. Skydd mot överspänning åstadkommes vanligtvis med en komponent som begränsar spänningen till skyddsområdet genom att tillhandahålla en lågimpediv väg. Detta visas med spänningsbegränsningen (voltage clamp) i fig 1.

Fig 1. Arbetsspänningsområden för integrerad krets och ESD-skyddskomponenter.

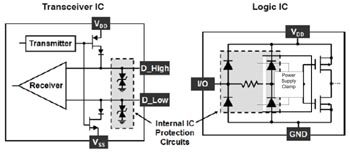

Exempel på ESD-konstruktion för I/O-anslutningar på en integrerad krets visas i fig 2. På den vänstra sidan i fig 2 finns spänningsbegränsare på ingångsanslutningen som ger en lågimpediv resistans till ICns jordbuss om spänningen överstiger det normala spänningsområdet. Det skyddar den känsliga ingången mot överspänning- och ström. Dessa spänningsbegränsare kan vara enkla zenerdioder, som framgår av figuren, eller specialkonstruerade nMOS-transistorstrukturer.

En annan vanlig metod är att använda ”styrdioder” som ”klampar” (clamp, d v s låser fast mot…) mot kraftaggregatets matningsspänning, så som visas i högra delen av fig 2. En negativ spänning på I/O-anslutningen i förhållande till jord kommer att ledas genom de styrdioder som är klampade mot jord för att motverka påfrestning på ingångarna.

En positiv spänning i förhållande till jord kommer att gå genom klampdioderna till VDD och vidare till matningsledningen. En klampdiod mellan VDD och jord kommer då vid överspänning att leda strömmen från VDD till jord.

Kraftaggregatsskyddet kan vara en enkel zenerdiod eller en aktiv krets som känner av oväntade spänningar mellan VDD och jord (GND) och som slår till en stor transistorswitch mellan VDD och jord för att åstadkomma en lågimpediv väg. Denna kretslösning fungerar på liknande sätt för överbelastning mellan I/O- anslutningen och VDD.

De två uppsättningarna styrdioder och motståndet mellan dem, i den högra delen av fig 2, är en del av en strategi som kallas primär- och sekundärskydd. Det primära skyddet är en uppsättning dioder nära I/O-anslutningen och är avsedda att ta hand om det mesta av överlastströmmen. Det sekundära skyddet är en uppsättning dioder nära respektive MOS-transistors känsliga gate. En viss överlastström kommer att gå igenom det sekundära skyddet. Men motståndet kommer inte bara att hjälpa till att begränsa strömmen till det sekundära skyddet. Spänningsfallet över motståndet hjälper även till att slå till det primära skyddet. Denna typ av skydd kommer vi också att granska när vi diskuterar skydd på systemnivå.

Fig 2. Vanlig intern ESD-skyddskretslösning.

En stor skillnad mellan ESD-skydd för integrerade kretsar och ESD-skydd för system är storleken på överlast. ESD-skydden i de flesta integrerade kretsar är avsedda att garantera att kretsen kan hanteras med högt utbyte i en ESD-kontrollerad produktionsmiljö där ESD-händelser är sällsynta och av låg styrka.

Idag är ESD-målet för moderna integrerade kretsar 1000 V HBM och 250 V CDM. Maximal ström för 1000 V HBM är ungefär 0,67 A med 150 ns avklingningstid medan CDM-strömmar kan vara flera ampere men bara ha varaktighet på några ns. Detta kan jämföras med 30 A med en varaktighet på 50 ns för en typisk överlast på 8 kV enligt IEC 61000-4-2, den vanligaste standarden för ESD-testsystem.

Det är uppenbart att I/O-anslutningarna för en modern integrerad krets inte kan klara nivån på en ESD-puls på systemnivå utan speciella konstruktionshänsyner.

Om skillnaden mellan ESD-test och -konstruktion av integrerade kretsar för säker hantering och ESD-test och -konstruktion på systemnivå i huvudsak är en fråga om magnitud, varför då inte konstruera ESD-systemsnivåtålighet på varje I/O-anslutning? Det gäller anslutningar som USB, Ethernet, HDMI och Display Port. I vissa fall är det görligt, men ofta inte.

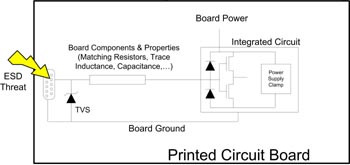

ESD-skyddsstrukturer kan inte skalas till mindre yta med små geometrier. Systemnivå-ESD-strömmar är höga och kan inte skalas ner till de nyare generationernas geometrier. Ungefär samma kiselyta behövs för att konstruera ett ESD-skydd på systemnivå med en modern teknologi som i en äldre. Kostnaden i form av yta är mycket högre i nya teknologier vilket medför att kostnaden för systemnivå-ESD-skydd ökar när teknologin blir mer avancerad. Dessutom är det för höghastighetsdata nödvändigt att ha mycket låg kapacitans i skyddskretsarna. Detta kan vara svårt i de flesta moderna teknologier som typiskt har höga dopningsnivåer i kislet vilket ger höga kapacitanser. Att använda ESD-skydd på kretskortsnivå som i TVS-enheten i fig 3 är därför att föredra.

ESD-skyddskomponenter

Systemkonstruktörer kan välja mellan många olika alternativa skyddsprodukter beroende på tillämpning och typ av förväntade påfrestningar.

Fig 3. Exempel på ESD-skydd på ett kretskort.

Ett exempel är metalloxidvaristorer (MOV). En MOV reagerar snabbt på transienter men deras höga kapacitans utgör en påtaglig extra last på signalledningarna. TSPD (Thyristor Surge Protection Devices) används ofta för skydd I telekom- och Ethernetutrustningar för att skydda mot ESD-påfrestningar på grund av deras stora strömhanteringsmöjligheter men de är ofta för lågsamma och har tillslagsspänningar som är för höga för att vara effektiva som ESD-skydd.

Polymerkomponenter som ESD-skydd används ibland på höghastighetsdataledningar beroende på dess låga kapacitans men de har ofta mycket höga tillslagsspänningar och deras begränsningsspänningar är ofta flera gånger högre än vad moderna integrerade kretsar kan tåla. Karakteristik för Polymer IV visas i fig 1. I de flesta medel- och lågeffektstillämpningar används vanligtvis kiselbaserade TVS-dioder (Transient Voltage Suppression) för ESD-skydd.

TVS-dioder

Användningen av TVS-dioder framgår av fig 3. TVS-komponenten placeras nära I/O-anslutningen. I en ideal situation slår TVS-komponenten till innan den integrerade kretsens interna funktioner och kortsluter störningsströmmen till jord. I praktiken blir det ofta en strömdelning mellan TVS-komponenten och ESD-skyddskretsarna i den integrerade kretsen. Detta arrangemang liknar mycket resonemanget med primärt och sekundärt ESD-skydd på den integrerade kretsen som disskuterades tidigare och visades i fig 2.

TVS-komponenter på kretskortet har en fördel framför ESD-skydd i den integrerade kretsen eftersom egenskaper som transinduktans och matchade motstånd kan användas som en del av ESD-skyddsstrategin och begränsa ESD-strömmen till den integrerade kretsen och ge ytterligare spänningsfall vilket hjälper till att slå till de primära ESD-skyddskretsarna på kortet.

ON Semiconductor tillverkar en rad olika TVS-komponenter för många tillämpningar och är konstruerade för att ha marknadsledande låga begränsningsspänningar.

Diodbaserade TVS-komponenter har en fördel gentemot metalloxidvaristorer och polymerbaserade ESD-skyddsprodukter. MOV och polymer har alltid symmetriska egenskaper för positiva och negativa påfrestningar. TVS-komponenter kan konstrueras med antingen symmetriska eller asymmetriska egenskaper. Enkla zenerdioder har asymmetriska egenskaper och leder i framriktningen med vanligt diodframspänningsfall och i backriktningen med zenerdiodsgenombrottsspänning. Detta är idealiskt för att skydda noder som bara har en polaritet som 0 till 3,3 V. Motkopplade dioder har symetriska egenskaper och ger samma spänningsgenombrott (diod + zenerspänning) för både positiv och negativ polaritet. Detta är idealiskt för att skydda noder som är symetriska kring 0 V som -3,3 V till +3,3 V.

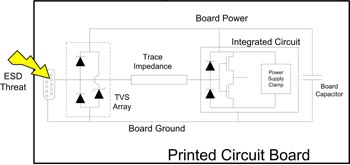

Avkoppling i kraftaggregat

Grupper med ESD-skydd kan ta med avkopplingskondensatorer i kraftaggregat som en del i skyddsstrategin. Vid ESD-frekvenser blir de keramiska avkopplingskondensatorerna i µF-området en lågimpediv impedans till jord. Styrdioderna i en TVS-grupp kan styra ESD-strömmen till jord eller till matningsledningarna på kortet och påtagligt minska spänningstransienterna på kortet som framgår av fig 4. Zenerdioder i TVS-gruppen kan ytterligare begränsa spänningstransienterna. Zenerdioder inbyggda i gruppen kommer också ha mycket låg induktans och kommer därför bli mycket effektiva att eliminera induktiva spänningsspikar som kan uppträda vid en ESD-händelse. För att vara effektiva måste kondensatorerna på koret monteras nära TVS-gruppen och både TVS-gruppen och kondensatorerna måste placeras så att de inte får högimpediva anslutningar som långa smala ledningar. ON Semiconductor tillverkar TVS-komponenter som passar många tillämpningar. Många är avsedda för specifika tillämpningar och är konstruerade för enkelt kortmontage.

Fig 4. Exempel på en TVS-grupp och avkopplingskondensatorer som en del av en ESD-skyddsstrategi.

Skydd av höghastighetsdataledningar

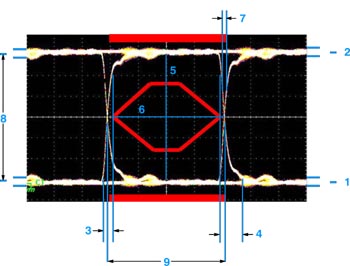

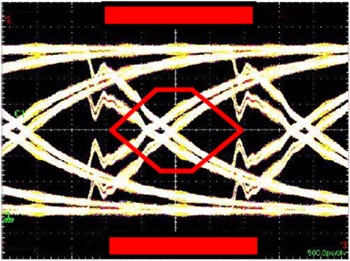

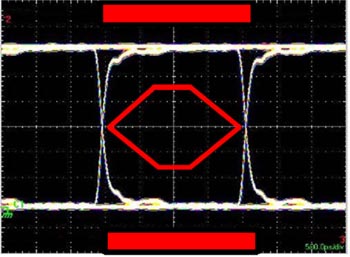

När TVS-dioder används för att skydda höghastighetsdataledningar kommer den tillhörande kapacitansen att inverka menligt på signalen och medföra datafel. I diagrammen i fig 5 och 6 jämförs en USB2-signal utan skydd och med en TVS-diod med kapacitansen 65 pF och visar på hur kapacitiv last inför distorsion på signalflankerna. Spåren som passerar USB2-masken i fig 6 visar på oacceptabel signalintegritet när en kapacitiv last påföres. Konstruktören måste hitta ESD-skyddslösningar som kan skydda känsliga ledningar utan att införa signalpåverkande kapacitans.

Fig 5. Ögondiagram för en USB2.0-dataledning utan ESD-skydd.

Fig 6. Ögondiagram för en USB2.0-dataledning med en ESD-diod med kapacitansen 65 pF.

Fig 7 visar en USB2.0-höghastighetssignal med ON Semiconductors snabba TVS-diod ESD9L som har ultralåg kapacitans på 0,5 pF. Diagrammet visar inte på några påtagliga förändringar på medelvärdet av logisk 1 eller 0 eller i signalernas stig- och falltider viket visar att komponenten har försumbar påverkan på dataintegriteten.

Fig 7. Diagram för USB2-dataledning skyddad av On Semiconductor ESD9L TVS-diod med kapacitansen 0,5 pF.

Bedöm ESD-prestanda

ESD-egenskaper hos elektroniska komponenter kan karaktäriseras genom att mäta med en transmissionsledningspuls (Transmission Line Pulse, TLP). Den standardiserade pulslängden 100 ns och strömmen 40 A som används i TLP motsvarar rätt väl pulslängden och strömmen som uppstår vid ESD-händelser. TLP kan tillämpas för ESD-systemnivå enligt IEC 61000-4-2 och ANSI/ESDA/JEDEC JS-001-2011 för HBM-test (Human Body Model).

Ett TLP-system kan användas för att generera I-V-kurvor i vilka varje datapunkt är från en puls vars varaktighet och strömamplitud har samma nivå som ESD-händelser på systemnivå. Dessa I-V-kurvor, och parametrar man hämtat från dem som dynamisk resistans och spänningsintercept, kan användas för att jämföra egenskaper hos olika TVS-enheter och kan användas för att förutse prestanda i en kretslösning.

ESD-skyddade små strukturer

De senaste CMOS-tillverkningsteknologierna möjliggör många framsteg för integrerade kretsar som minskad kiselstorlek, lägre arbetsspänning och effektförbrukning samt förbättringar i hastighet och funktioner.

Konstruktionsdimensionerna minskar men ESD-spänningarna förblir opåverkade och utgör ett ökat hot mot dagens högkänsliga kretsar. En mångfald tillämpningsråd och ett brett spektrum av dedikerade skyddsenheter, däribland lågkapacitiva enheter för höghastighetstillämpningar, ger konstruktörer de verktyg de behöver för att skapa tillförlitliga produkter som uppfyller de svåraste testkriterier.

Filed under: Avstorning