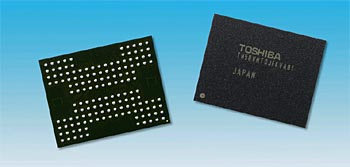

16 stackade chip från Toshiba

Toshiba har utvecklat en teknik för att stacka upp till 16 NAND-chip med hjälp av vior genom chipet (TSV). Prototypen kommer att visas vid Flash Memory Summit 2015 i Santa Clara nästa vecka.

Tidigare har stackade NAND-chip kontakterats med hjälp av trådbondning. Med TSV-tekniken kontakteras i stället chipen direkt genom substraten, vilket ger snabbare kommunikation och lägre energiförbrukning.

På det här sättet är det möjligt att klara I/O-hastigheter över 1 Gbit/s, vilket är mer än tidigare flashminnen med låg matningsspänning. Toshiba matar kärnan med 1,8 V och I/O-enheterna med 1,2 V. Tillsammans ger det uppskattningsvis en halvering av energiförbrukningen vid skriv-, läs- och I/O-operationer.

Filed under: Utländsk Teknik